Page 3 of 3

Re: PID Integrator Hold

Posted: Sun May 24, 2015 12:49 pm

by fromage

Hi Claire,

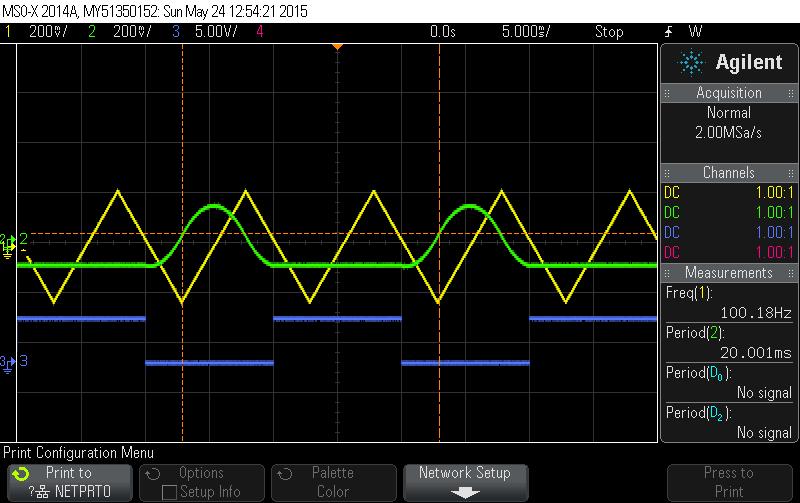

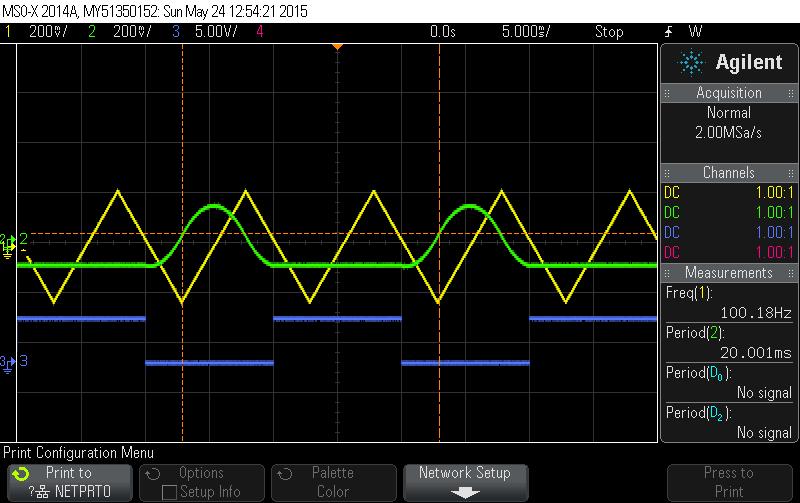

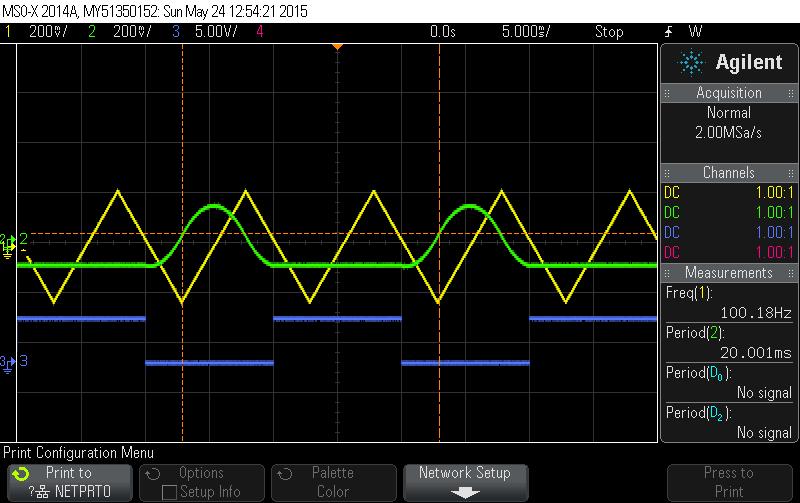

I teste the hold TTL input today and it worked perfectly (see screenshot ).

yellow:inputsignal

yellow:inputsignal;

green:integrator output;

blue:TTL-signal

Thanks for sharing your code and for your help!

Best wishes Florian

Re: PID Integrator Hold

Posted: Mon May 25, 2015 1:02 am

by ClaireE47

That looks awesome! I'm so glad

All the best,

Claire

Re: PID Integrator Hold

Posted: Fri Jun 02, 2017 3:44 am

by amin

Hey Claire,

it is interesting topic for me that you successfully made PID algorithm.

i already learned about generate .bit and .bin using vivado and labtools

Now, i want to try to make PID.

I did try download your dropbox link, but the dropbox link is disabled.

please, could you upload again

Re: PID Integrator Hold

Posted: Mon Jun 26, 2017 11:39 pm

by ThomasB

Hi Claire

I am also interested in your PID sample/hold-code -- the results from fromage looks good!

I know the post is old. Unfortunately, no one else has touched the subject since (as far as I can find).

As being new to RedPitaya and FPGA, I would be very happy if you could share your code once again

I looked at the code you posted so far in the thread, but I would like to see your final code.

So Claire, I hope you are still there... Even just the FPGA code without the C and HTML would be good!

Best,

Thomas

Re: PID Integrator Hold

Posted: Tue Jun 27, 2017 12:05 am

by ClaireE47

Hi Amin and Thomas,

Sorry about the dropbox confusion - I must have removed the code at some point. It's been a while since I've thought about this project but I think that this should be sufficient code... If there's anything missing just give me a yell and I'll have a look.

Cheers,

Claire

Re: PID Integrator Hold

Posted: Wed Sep 27, 2017 1:53 pm

by XueshiGuo

Is there any reason that the hold signals have to go through house keeping module, can I directly use two pins in Expansion connectors "[8-1:0] exp_p_io" instead?

Re: PID Integrator Hold

Posted: Mon Oct 23, 2017 9:52 am

by amin

ClaireE47,

I already copy your FPGA folder to tmp in git of redpitaya in eclipse.

and then i search file bit that i found red_pitaya_top.bit in

Code: Select all

root@rp-f04d8a:~/tmp/FPGA/release1/fpga/vivado/red_pitaya.runs/impl_1#

i tried compile this red_pitaya_top.bit using

Code: Select all

cat /tmp/FPGA/release1/fpga/vivado/red_pitaya.runs/impl_1/red_pitaya_top.bit >/dev/xdevcfg

But i did not get signal respon in the output of DIO0_P and DIO1_P. i tried connect these output using oscilloscope.

Is it correct if i just copy into tmp folder in respitory eclipse?

Can you explain step by step of how to copy into respitory redpitaya in eclipse?

Also can i edit this FPGA folder in vivado? I already open the RedPitaya_with_Hold\FPGA\release1\fpga\vivado\vivado.xpr in vivado 2016.3 but i cannot generate bit stream.

sorry i am still learn about vivado and linux

Sincerely,

Amin

Re: PID Integrator Hold

Posted: Tue Oct 24, 2017 5:16 am

by amin

ClaireE47,

I can generate bitstream your RedPitaya_with_Hold\FPGA\release1\fpga\vivado\vivado.xpr using vivado 2013.3.

after that i copy red_pitaya_top.bit from FPGA/release1/fpga/vivado/red_pitaya.runs/impl_1 into eclipse redpitaya/tmp.

But when i executed using scp

Code: Select all

red_pitaya_top.bit root@@192.168.11.25:/tmp

and

Code: Select all

cat /tmp/red_pitaya_top.bit >/dev/xdevcfg

, i only get respon blink led in LED0.

I did not get respon signal output in DIO0_P and DIO1_P.

Regards,

Amin