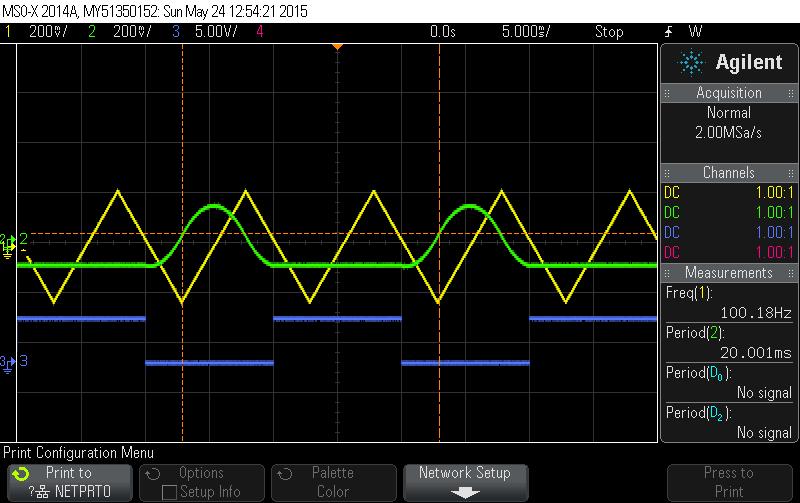

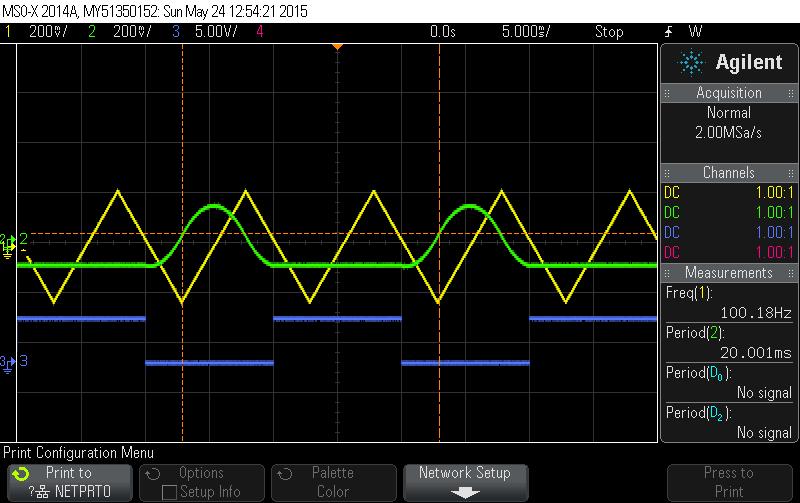

I teste the hold TTL input today and it worked perfectly (see screenshot ).

yellow:inputsignal; green:integrator output; blue:TTL-signal

Thanks for sharing your code and for your help!

Best wishes Florian

Hey Claire,ClaireE47 wrote:Hey, this has my edits to the C code (Applications/MyPID/src) and the HTML (Applications/MyPID/index.html) for the software trigger, and the Verilog edits (FPGA/release1/fpga/code/).

https://www.dropbox.com/sh/rwjmzs183ls9 ... AwFZa?dl=0

Code: Select all

root@rp-f04d8a:~/tmp/FPGA/release1/fpga/vivado/red_pitaya.runs/impl_1#Code: Select all

cat /tmp/FPGA/release1/fpga/vivado/red_pitaya.runs/impl_1/red_pitaya_top.bit >/dev/xdevcfgCode: Select all

red_pitaya_top.bit root@@192.168.11.25:/tmpCode: Select all

cat /tmp/red_pitaya_top.bit >/dev/xdevcfgUsers browsing this forum: No registered users and 25 guests